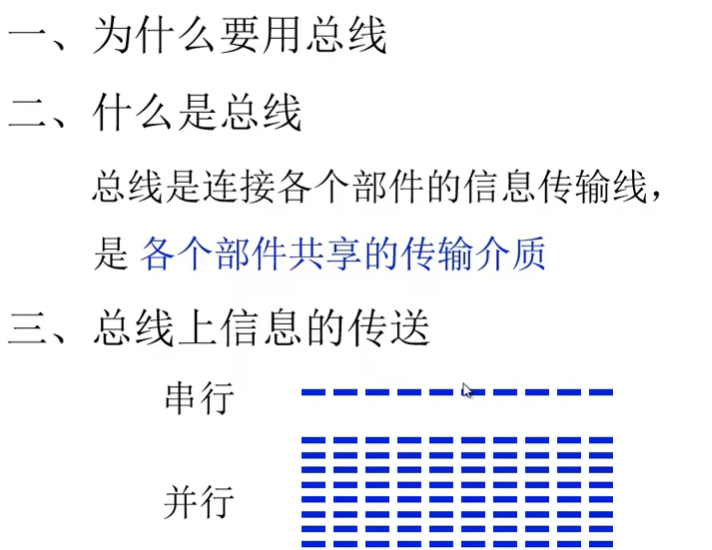

总线

总线的基本概念

并行传输容易出错,所以一般距离较短

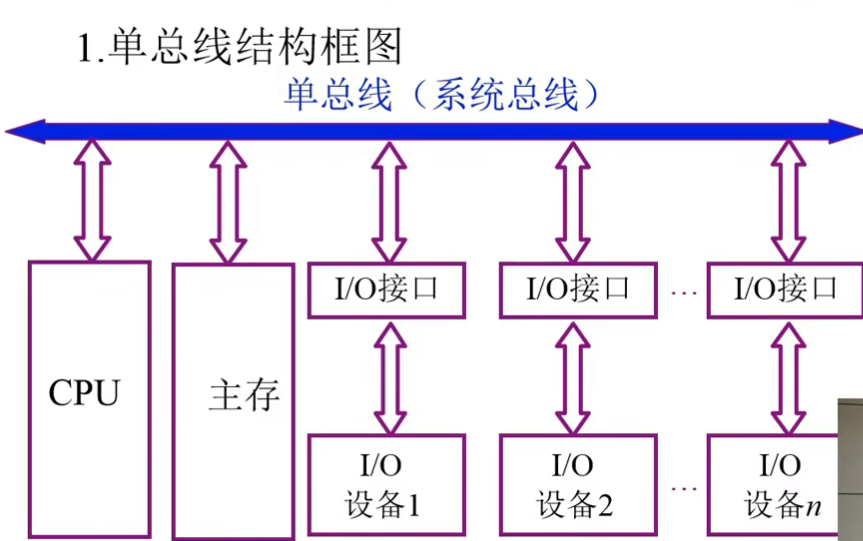

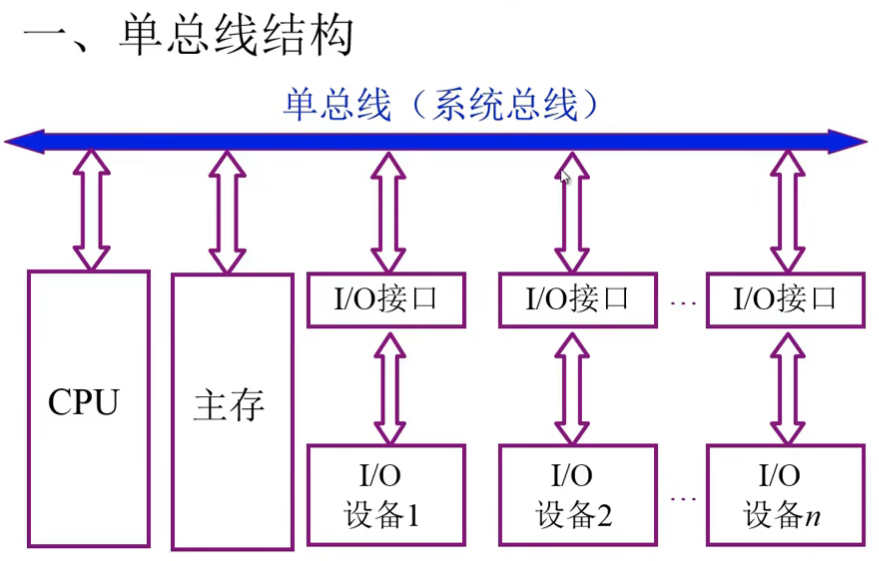

缺点:当主存和I/O进行信息传输时,CPU不能运行

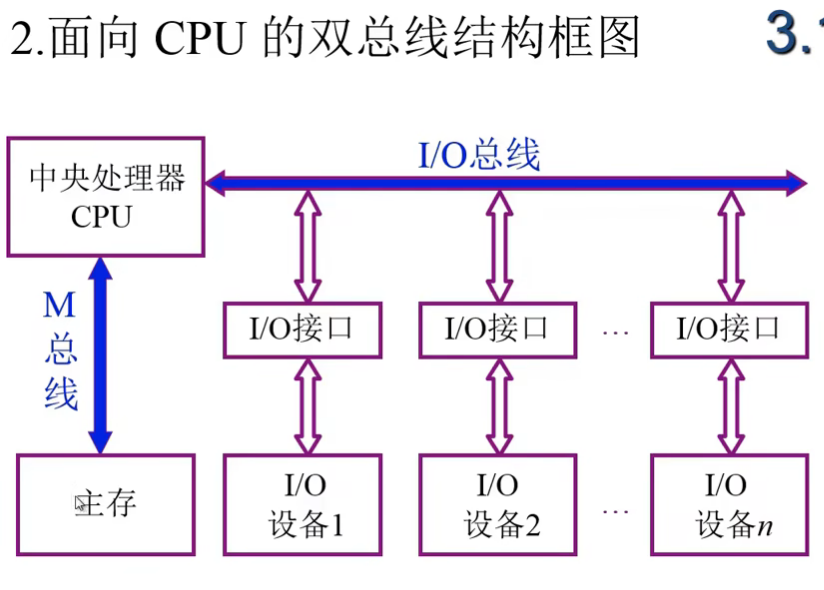

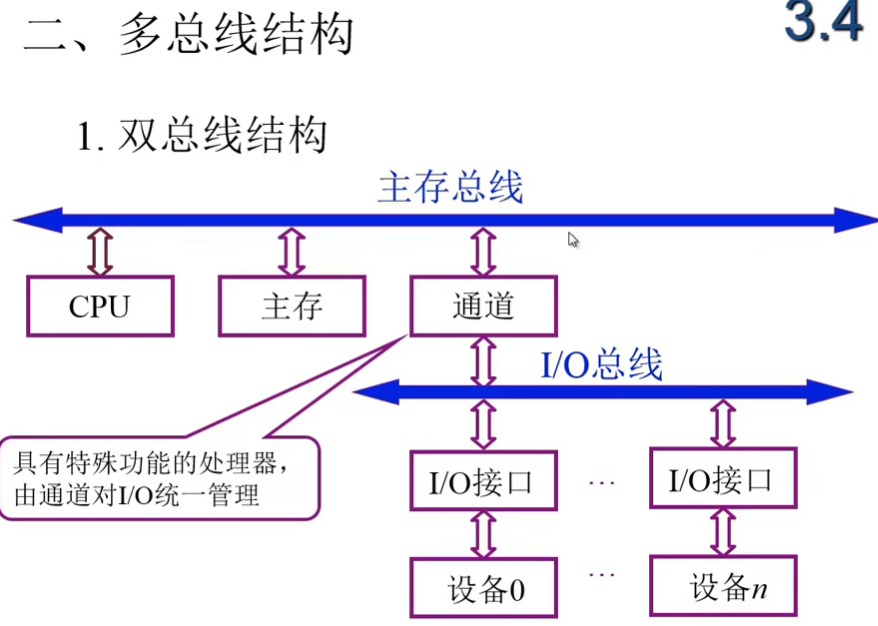

缺点:主存和I/O不能直接进行信息传输,需要打断CPU的执行程序的任务

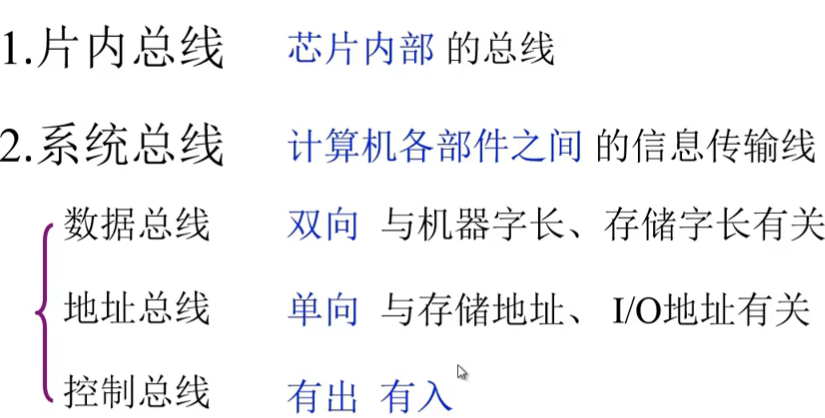

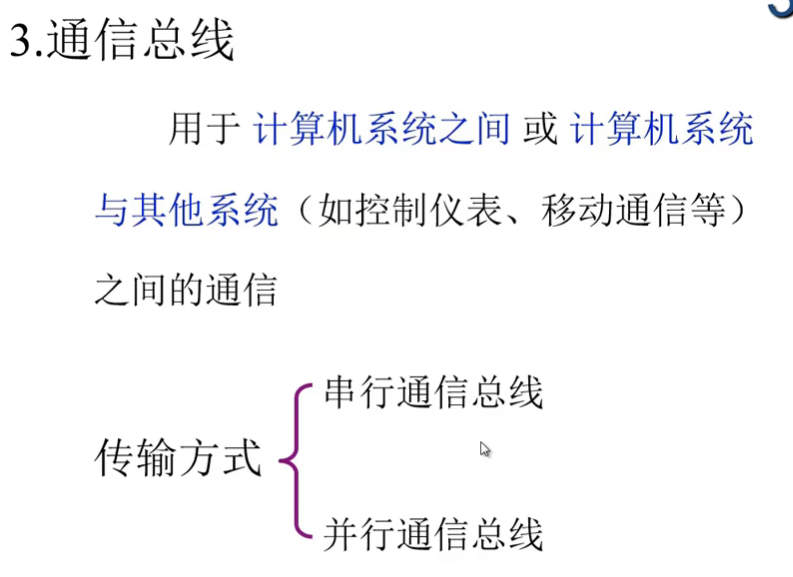

总线的分类

有出(CPU向外送的):存储器读、存储器写,总线允许,中断确认

有入(由I/O端口送给CPU):中断请求、总线请求

总线性能及性能指标

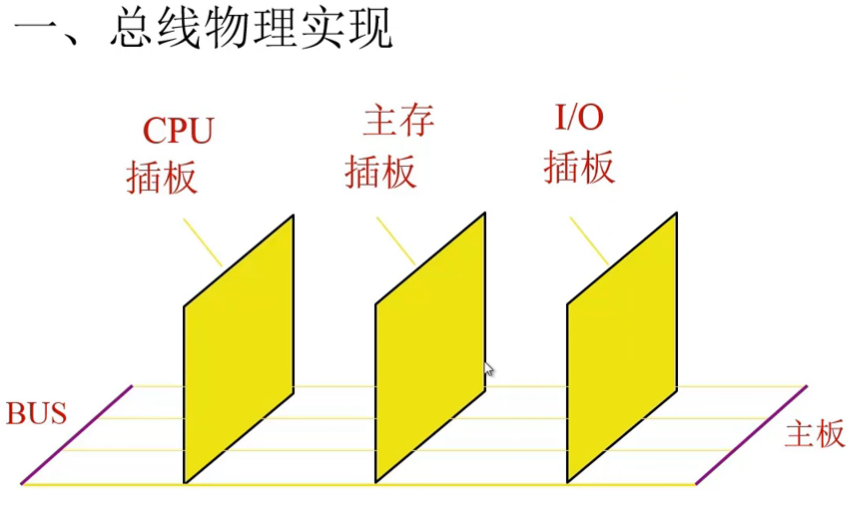

总线物理实现

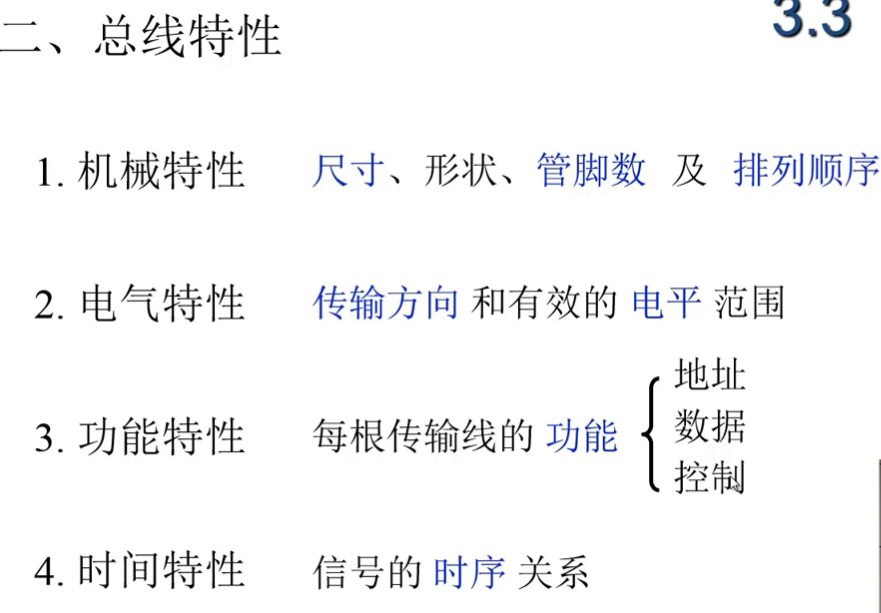

总线特性

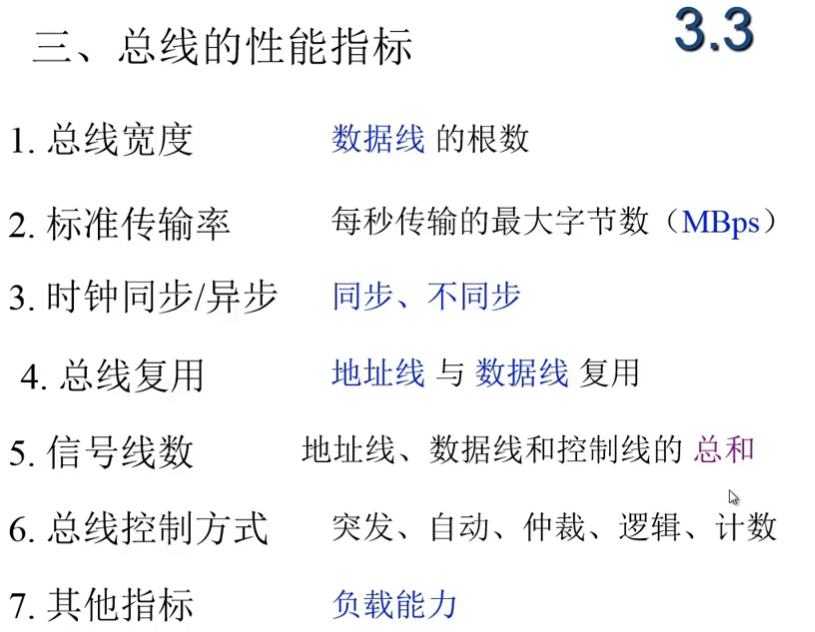

总线的性能指标

总线结构

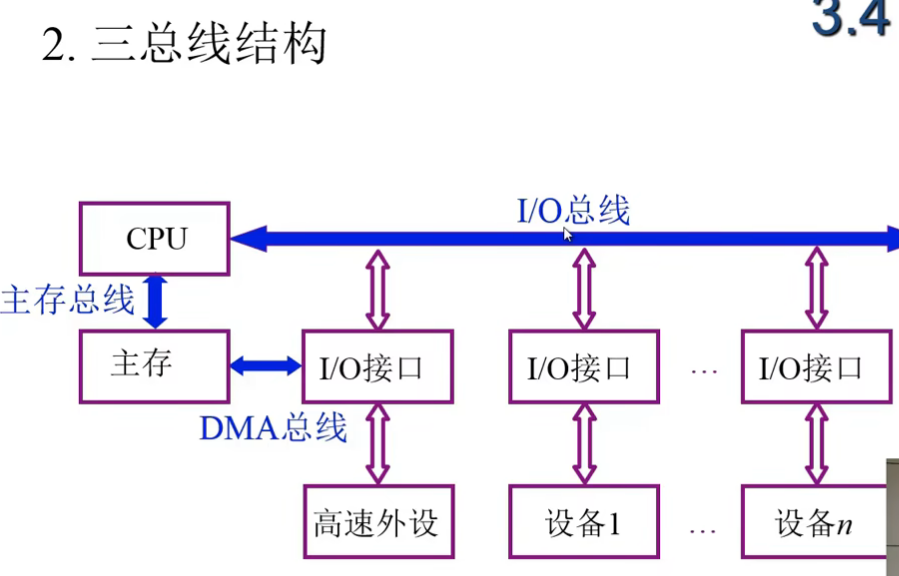

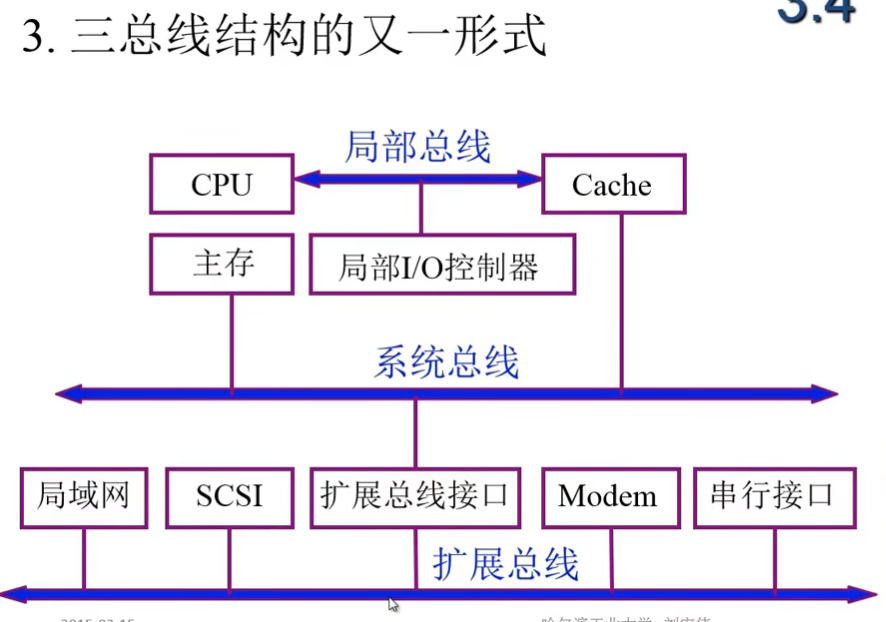

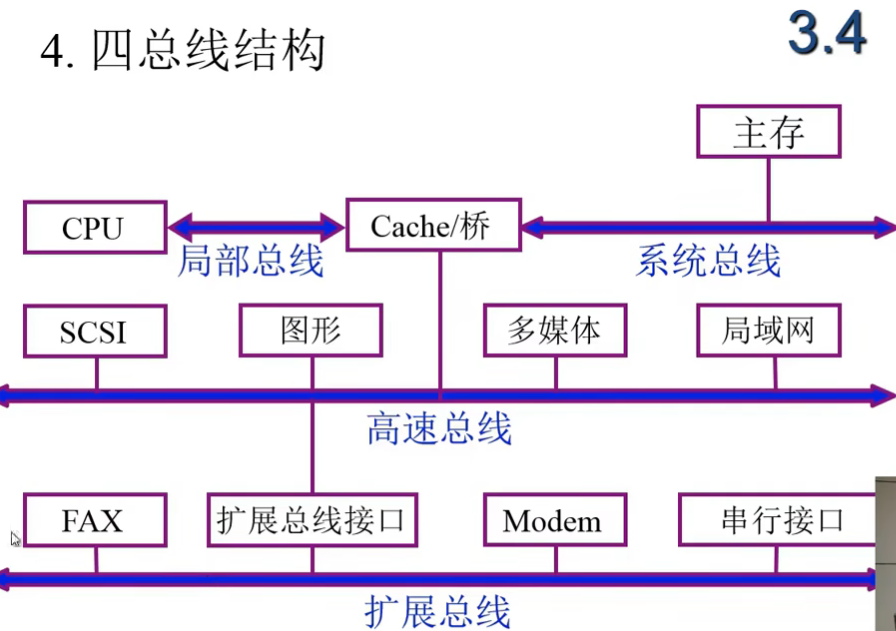

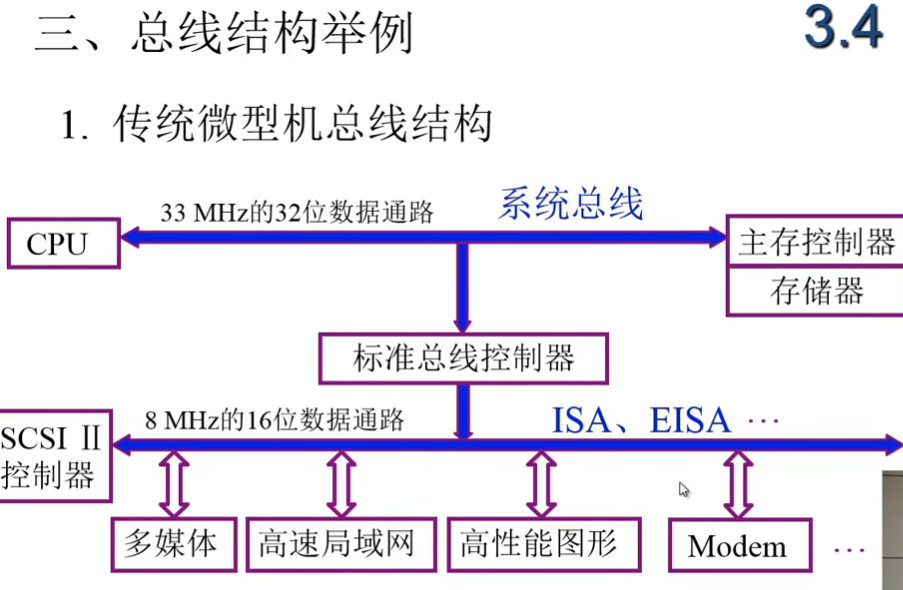

把高速设备和低速设备区分开,高速设备用高速总线进行组织,低速设备用扩展总线进行组织,使数据传输速率更高。

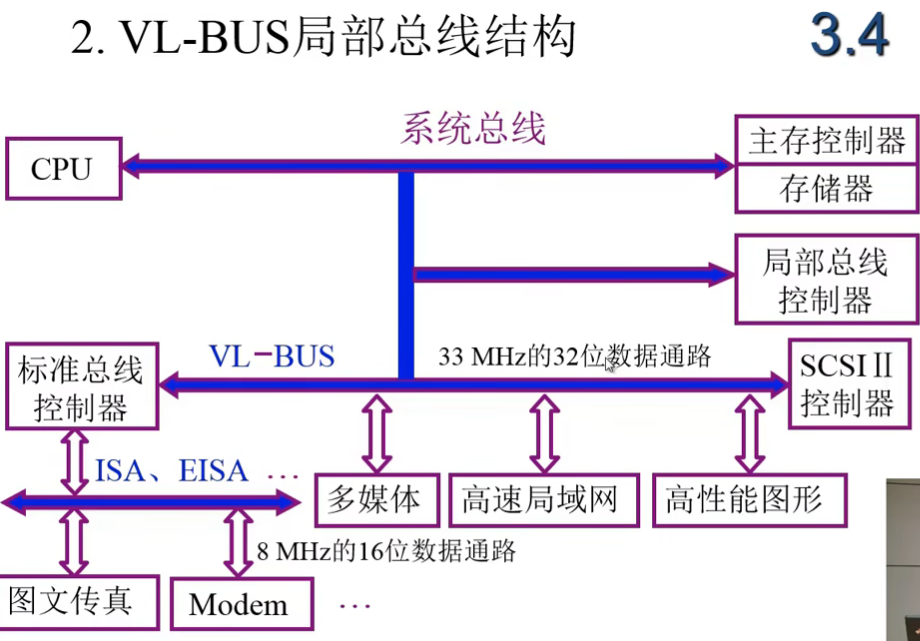

同样区分了高速设备和低速设备(VL-BUS连接高速,ISA、EISA连接低速)

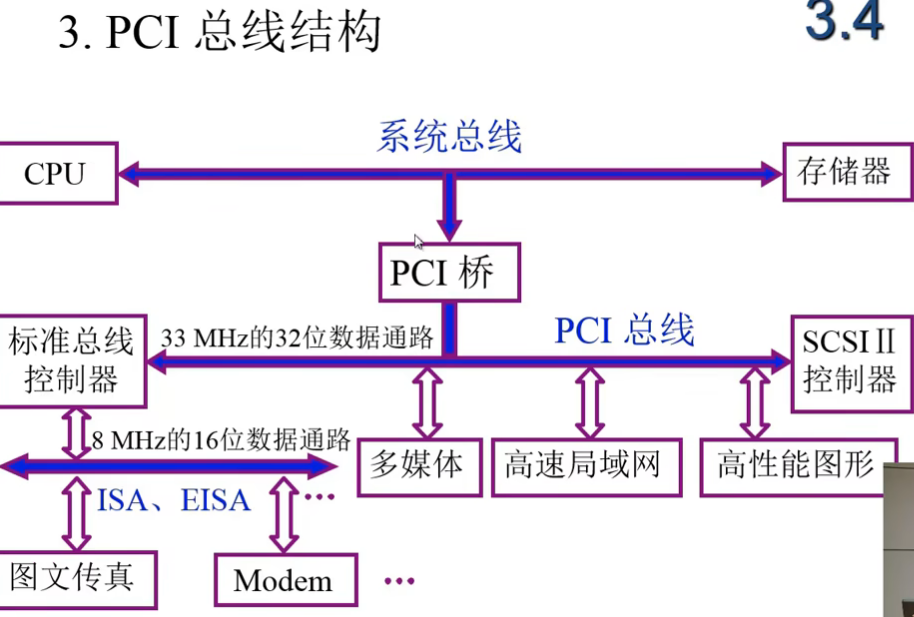

(PCI总线连接高速,ISA、EISA连接低速)

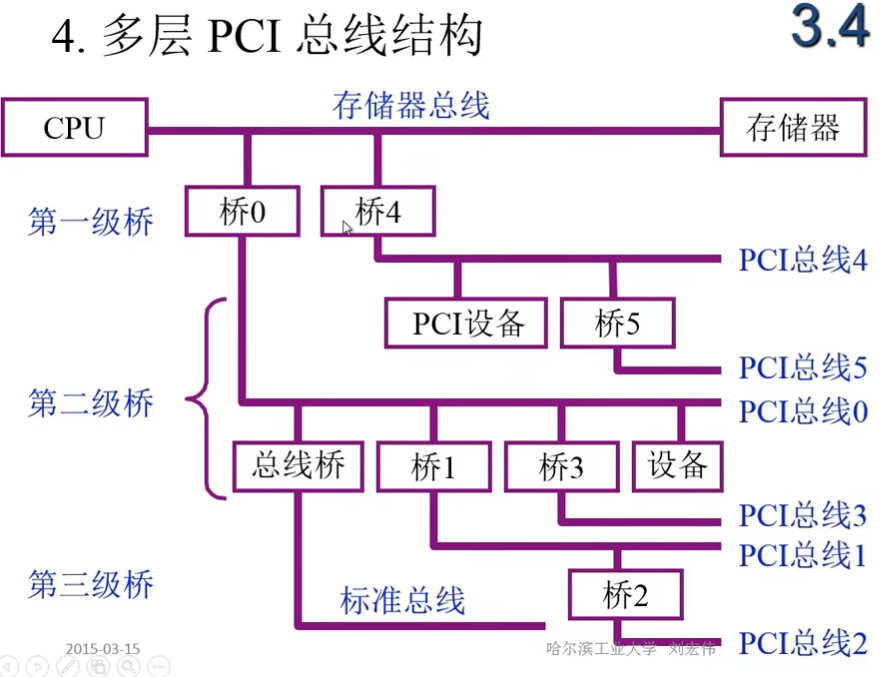

通过桥电路实现了总线的驱动能力的提高和总线的扩展

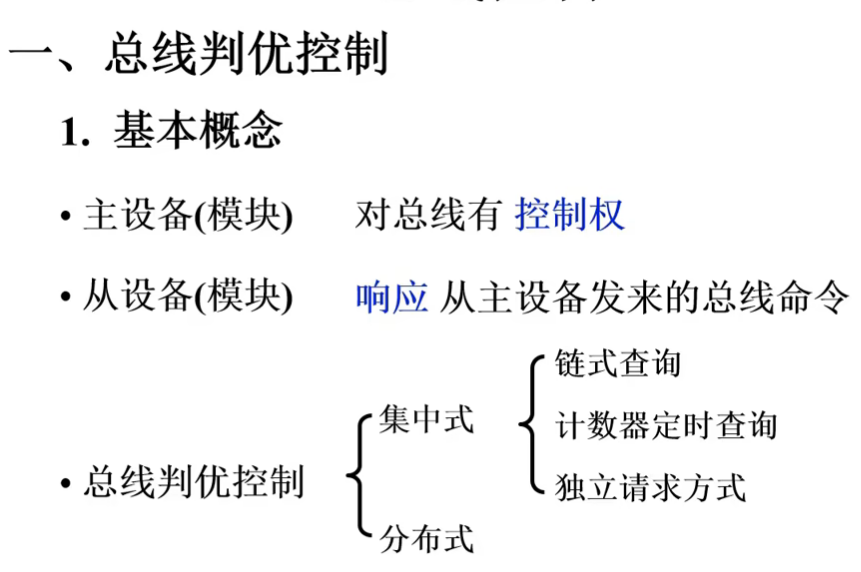

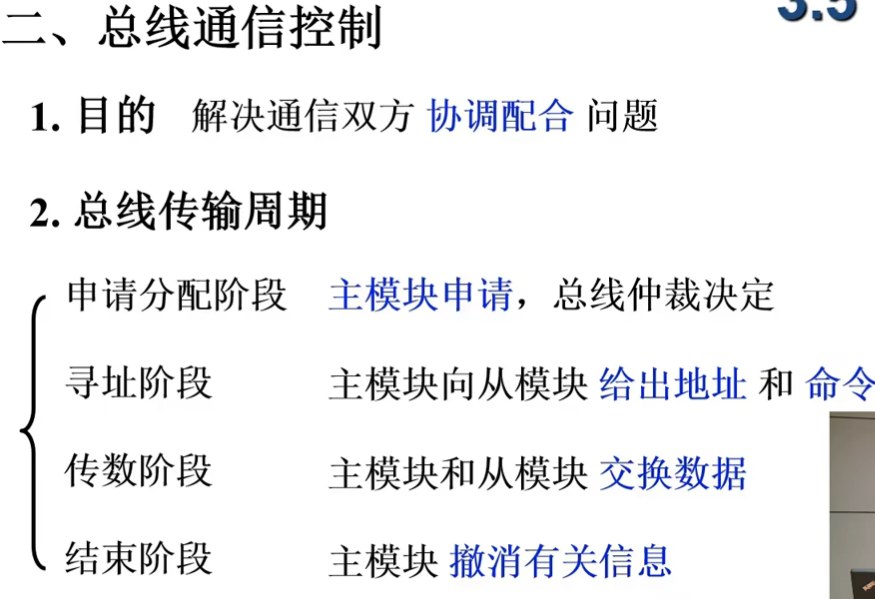

总线控制

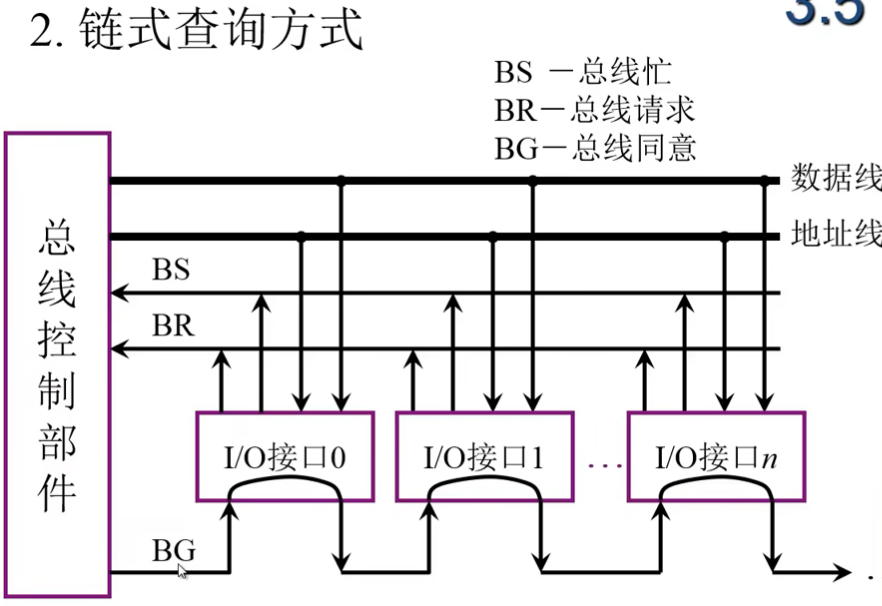

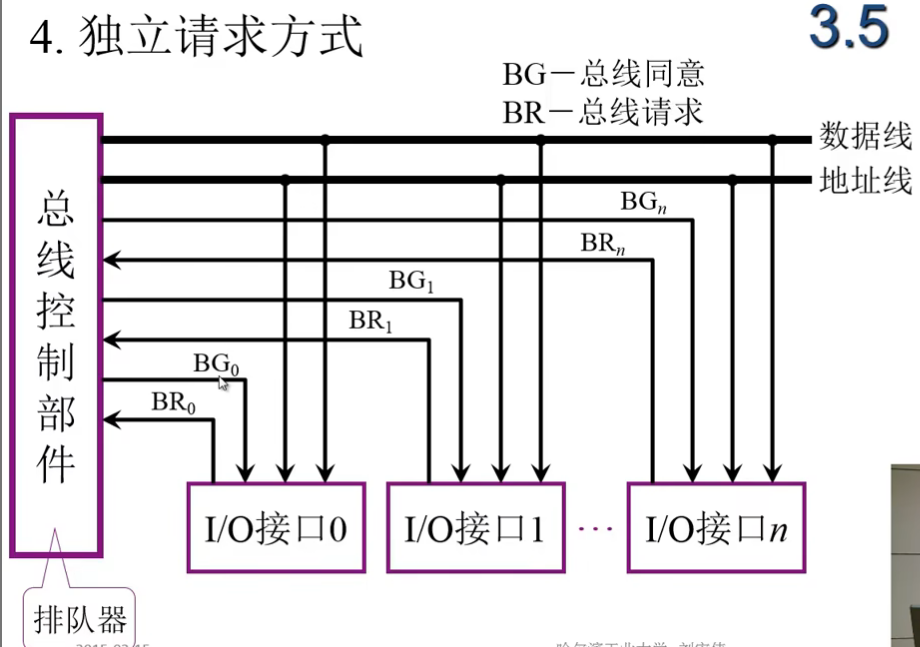

BG的连接顺序就是I/O接口的优先级顺序

优点:结构简单,增删设备容易,容易实现可靠性设计(比如增加一条BR线,防止出现问题)

缺点:某一处出现故障,信号无法继续向后传,后面的接口无法获得总线的使用权,所以对电路故障非常敏感

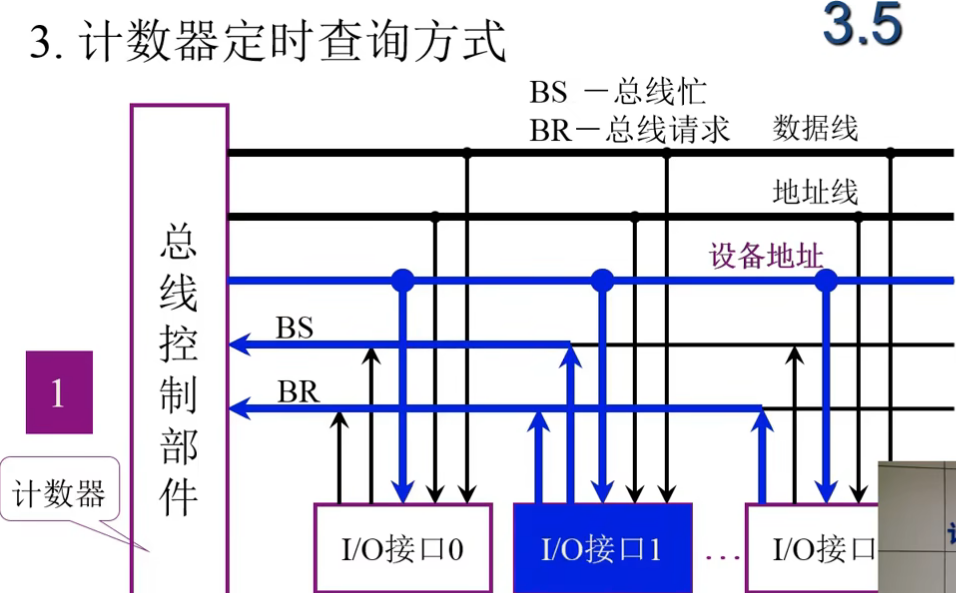

优点:优先级灵活(可以通过计数器来控制优先级)

优点:优先级灵活(可以通过排队器的设置来控制优先级)

缺点:需要的线数比较多

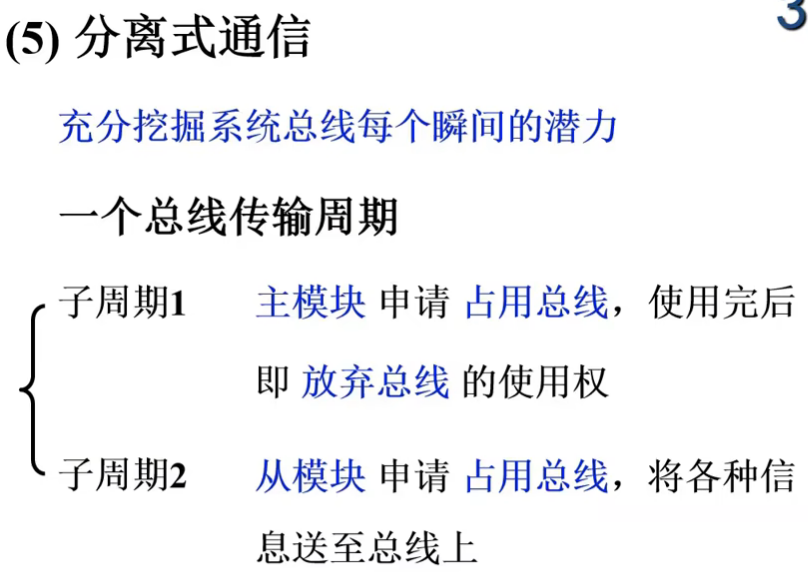

潜力

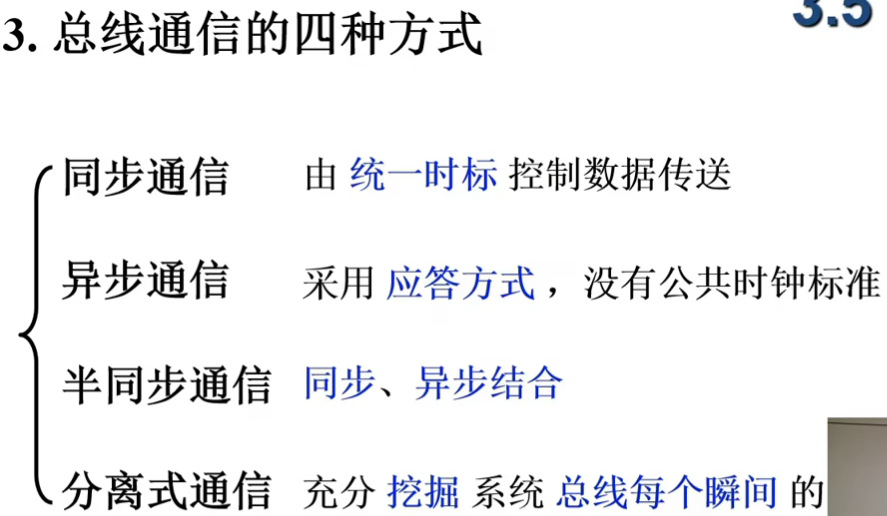

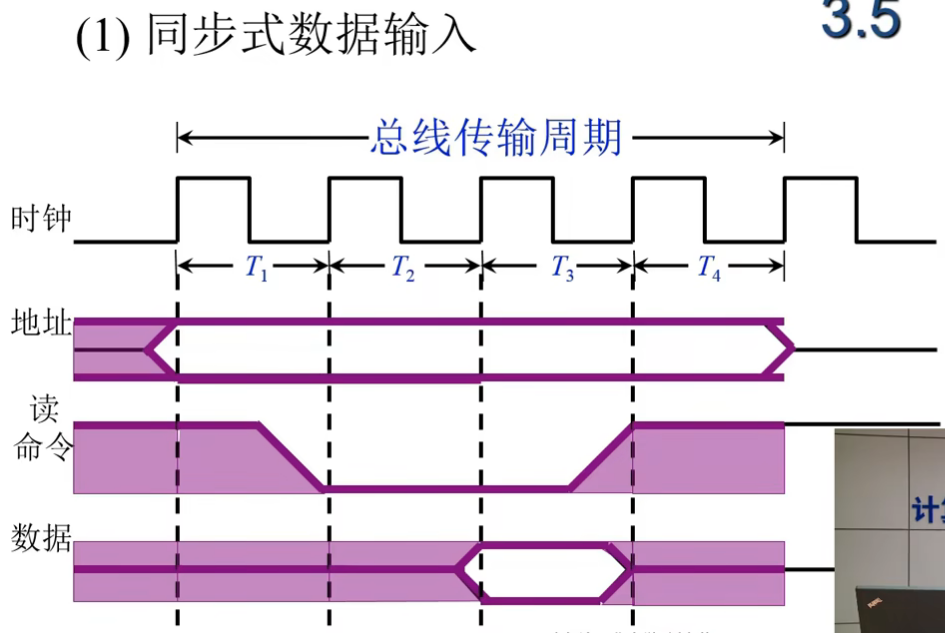

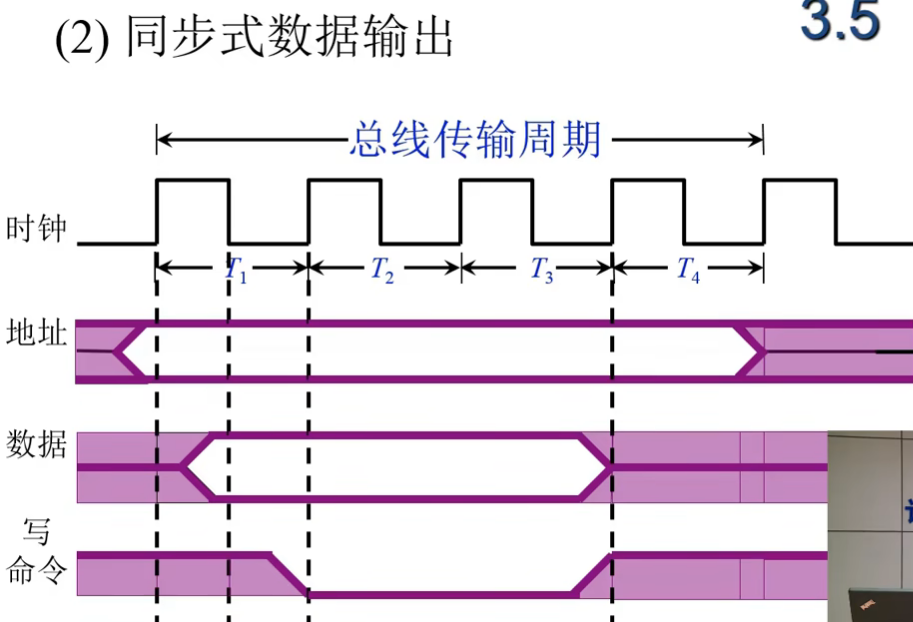

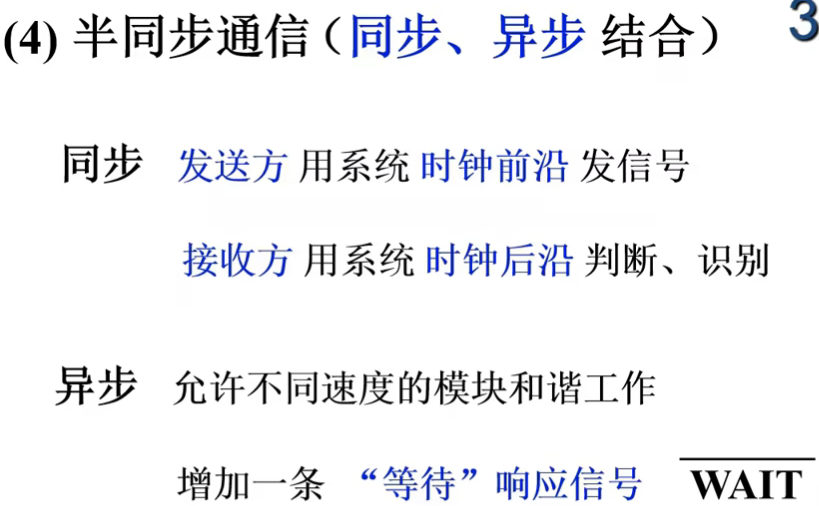

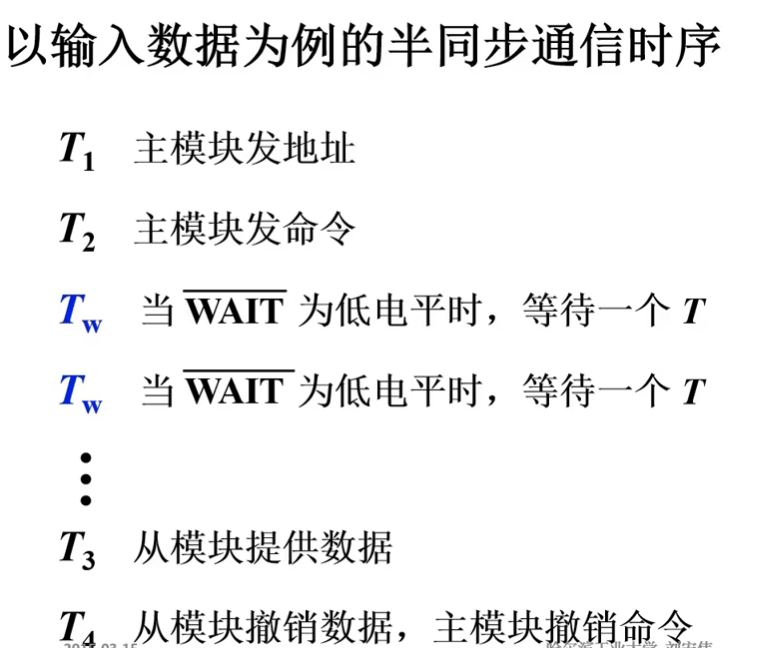

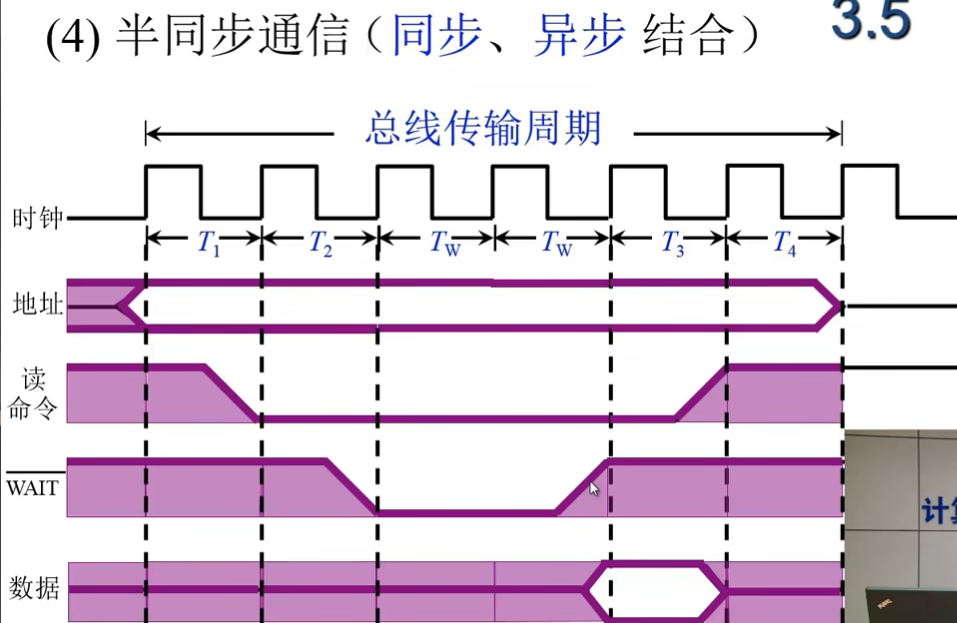

同步式适用于总线长度较短,而且各个模块存取时间比较一致的情况

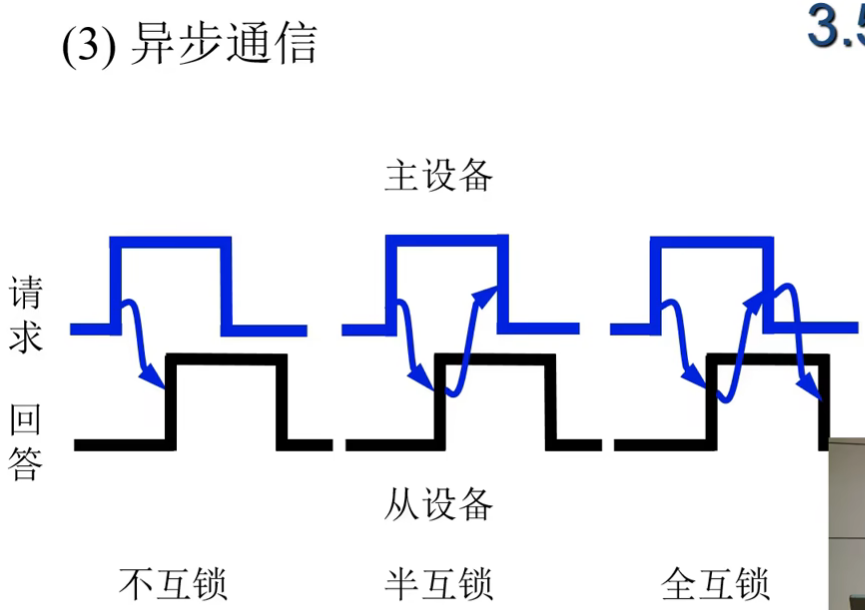

不互锁:主设备发出请求后一段时间后即使没有收到应答信号也会撤销信号,从设备发出应答信号后一段时间后即使没有收到撤销信号也会撤销应答信号

半互锁:主设备发出信号后一直等到收到应答信号才会撤回信号,从设备发出应答信号后一段时间后即使没有收到撤销信号也会撤销应答信号

全互锁:主设备发出请求后直到收到应答信号才会撤销信号,从设备发出应答信号后直到收到撤销信号才会撤销应答信号

异步通信可以完成可靠的数据传输

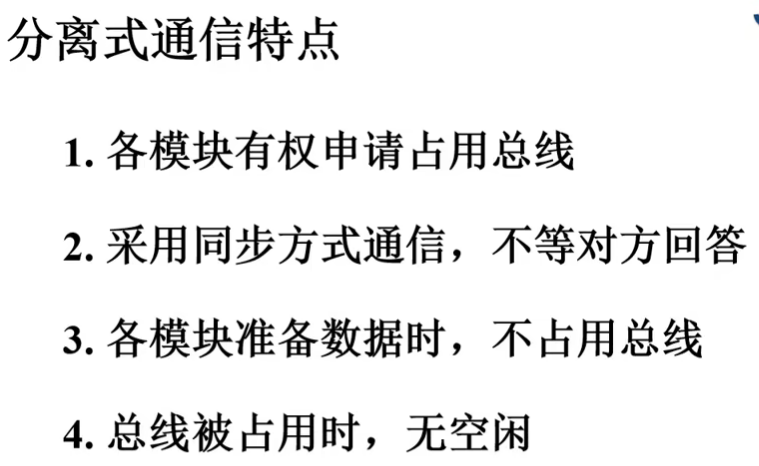

所有的模块都可以从从模块可以变成主模块

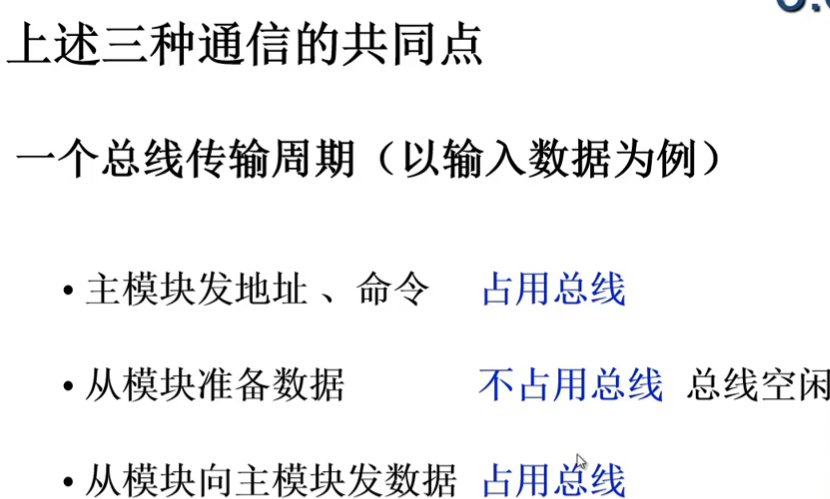

总线被占用时一定在进行数据通信或者在传输控制命令,充分利用了总线的带宽